What's your (single) point, youngster? Pg 70

**AUG** 2012

www.edn.com

Issue 14

EDN.comment Pg 10

Instrumentation amplifier input-circuit strategies Pg 20

Teardown Pg 22

Design Ideas Pg 55

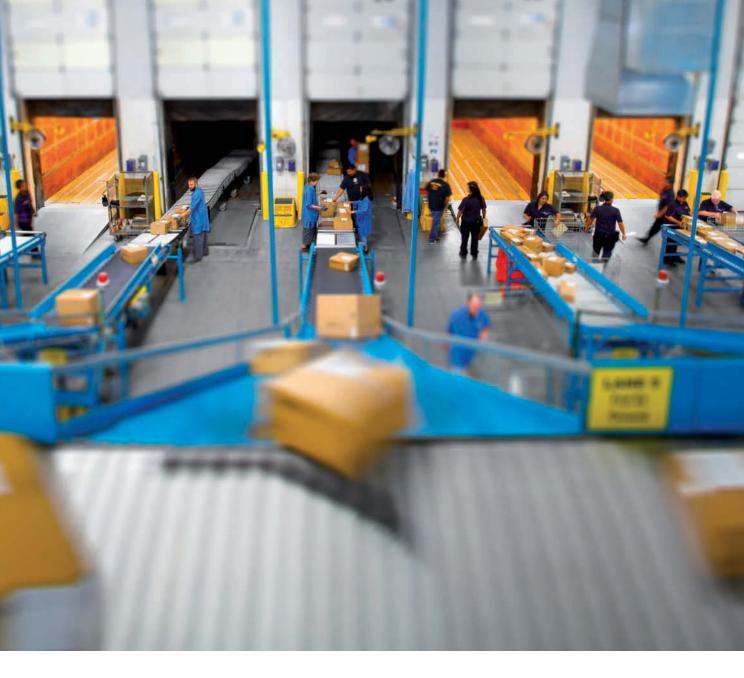

The limits of lean Pg 64

### **BEST OF CLASS: BROADEST OVERALL PRODUCT SELECTION**

SOURCE: 2012 DESIGN ENGINEER AND SUPPLIER INTERFACE STUDY, HEARST BUSINESS MEDIA ELECTRONICS GROUP, NORTH AMERICA

2 MILLION PARTS ONLINE 500+ INDUSTRY-LEADING SUPPLIERS NEW PRODUCTS ADDED DAILY

**TIP 1** For an inductor with the absolute maximum Q, pick one of these air core "Springs". They have flat tops for easy mounting and exceptional current ratings.

**TIP 2** If you prefer conventional chip inductors, you'll get the highest Q with our new ceramic

body 0402HP and 0603HP families. These tiny wirewound coils handle up to 2 times more current than the nearest competitor.

This new web tool finds inductors with the highest Q at your operating frequency

**TIP 3** Need to find coils with the best Q at your L and frequency? Our **Highest Q Finder** web tool tells you in just seconds. Click again to plot the L, Q, Z and ESR of up to 4 parts simultaneously.

**TIP 4** When it's time to build your prototypes, be sure to ask

us for evaluation samples. They're always free and we can get them to you overnight. To get started, visit www.coilcraft.com/Q

# Here are some high Q tips

# **EDN** contents

August 2012

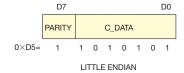

### Managing the 8- to 32-bit processor migration

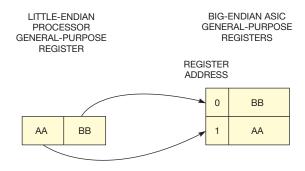

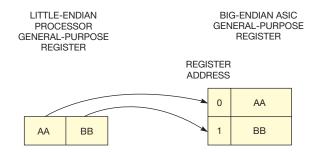

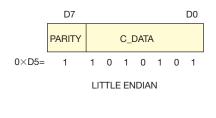

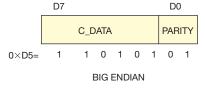

49 To prevent Lilliputian processor disparities from hatching a swarm of bugs, application developers working in C must keep native processor size and endianness in mind and write their code with an eye toward portability.

by Kevin King, Renesas Electronics America

IMAGE: ISTOCK

### DESIGNIDEAS

- 55 Quasistatic Spice model targets ceramic capacitors with Y5V dielectric

- 58 Microcontroller drives piezoelectric buzzer at high voltage through one pin

- 58 Circuit automatically switches off DMM

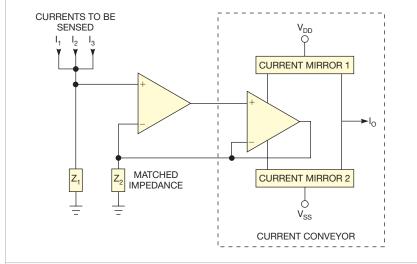

- 60 Reconstruct the input current in a grounded-impedance current sensor

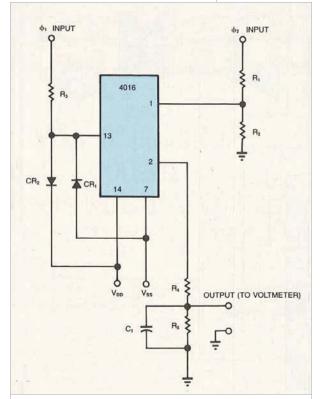

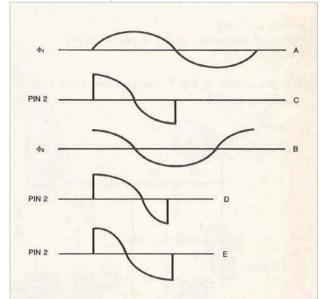

- 62 Simple circuit suits quadrature detection

- Submit your own Design Idea to edndesignideas@ubm.com.

[www.edn.com] AUGUST 2012 | EDN 5

### **Authorized Distributor**

Advanced **semiconductor** solutions to fuel your creativity.

Come to Mouser first for what's next from these industry leaders.

### contents August 2012

- 12 LED increases efficacy by 20%

- 14 Terahertz scanner on your smartphone?

- 16 Nordic offers BLE, ANT single-chip solutions

- 16 Printable conductive gel promises low-cost biosensors, energy storage

- 18 Voices: Finally, a hardware accelerator: Bolt's Ben Einstein on a leg up for hardware start-ups

### **DEPARTMENTS & COLU**

- EDN online: Join the conversation; Content; Engineering Community

- 10 **EDN.comment:** Next-gen "Edisons" doing just fine

- 20 **Baker's Best:** Instrumentation amplifier input-circuit strategies

- 22 Teardown: Volt's battery-stack manager aids Chevy's drive for safe power

- 28 Connecting Wireless: In wireless, MIMO's the word

- 30 **Mechatronics in Design:** "Mechatronify" common mechanisms

- 64 **Supply Chain:** The limits of lean

- 66 Product Roundup: RF and Wireless

- **Tales from the Cube:** What's your (single) point, youngster?

EDN® (ISSN# 0012-7515) is published semimonthly (January-June) and monthly (July-December) by UBM Electronics, 600 Community Drive, Manhasset, NY 11030-3825. Periodicals postage paid at Manhasset, NY, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 847-559-7597. E-mail: edn@omeda.com. CHANGE OF ADDRESS—Notices should be sent promptly to EDN, PO Box 3609, Northbrook, IL 60065-3257. Please provide old mailing label as well as new address. Allow two months for change. NOTICE-Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 3609, Northbrook, IL 60065-3257. CANADA POST: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to APC, PO Box 503, RPO West BVR CRE, Rich Hill. ON L4B 4R6. Copyright 2012 by UBM. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 57, Number 14 (Printed in USA).

Over 2500 Std. **DC-DC Converters**  Surface Mount From 2V to 10.000 **VDC** Output 1-300 Watt Modules Isolated/ Regulated/ Programmable Models Available Military Upgrades Available · Custom Models, Consult Factory Delivery-Stock to one week for sample quantities Call toll free 800-431-1064 in NY call **914-738-1400** Fax **914-738-8225** Electronics, Inc. 143 Sparks Ave. Pelham, N.Y. 10803 E Mail: info@picoelectronics.com www.picoelectronics.com

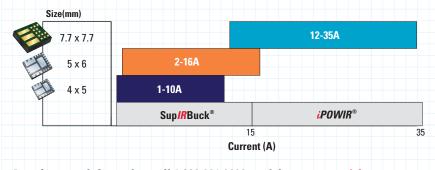

# **Easy POL Converter Design**

Online Tool Simplifies Sup/Rbuck® POL Design http://mypower.irf.com/Sup/Rbuck

### **Integrated Voltage Regulator Product Offering**

|        | 5V bias required |         |         | Integrated LDO |         |

|--------|------------------|---------|---------|----------------|---------|

|        | 1- 16Vin         | 1-21Vin | 3-27Vin | 1- 16Vin       | 1-21Vin |

| 1-3A   | IR3843W          |         |         |                |         |

| 4-6A   | IR3842           | IR3853  |         | IR3839*        | IR3897* |

|        | IR3842W          | IR3863  |         |                | IR3898* |

|        | IR3832W*         | IR3856  | IR3473  |                |         |

| 7-10A  | IR3831W*         | IR3859  |         | IR3838*        | IR3899* |

|        | IR3841           | IR3865  | IR3475  | IR3865         |         |

|        | IR3841W          |         |         |                |         |

| 11-16A | IR3840           |         | IR3476  | IR3837*        | IR3894* |

|        | IR3840W          |         | IR3477  |                | IR3895* |

| 16-35A | iP1827           |         |         |                |         |

|        | iP1837           |         |         |                |         |

\*DDR Tracking

for more information call 1.800.981.8699 or visit us at www.irf.com

### The Sup/Rbuck® Advantage:

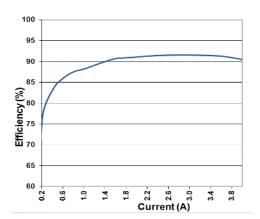

- Best in class efficiency

- Common footprint over wide load range for design flexibility

- Full featured and protected for easy on-board implementation

- Integrated controller, bootstrap diode,control FET and Sync FETKY

### The Tool Provides:

- Schematics

- Bill of Materials

- Simulation and Thermal Analysis

International

Rectifier

THE POWER MANAGEMENT LEADER

### JOIN THE CONVERSATION

Comments, thoughts, and opinions shared by EDN's community

In response to "Rounding errors, verification, and laziness," a blog post at www.edn.com/4391628, UD-00001 commented:

"Sorry to say, but it's not laziness; it tends to be a lack of education.

"During my university days, integer math was taught. Nowadays, it seems that algorithmic precision is no longer an issue: 'Hev. don't think: use float!'

"They are not even aware of the degree of incertitude. And in my current job in automotive

electronics, there often is quite a difference between the float results and precisely designed integer math—making the difference between superior and sluggish performance.

"But I understand; integer is not sexy."

### In response to "Revisiting the analog video decoder: brushing up on your comb filters," at

www.edn.com/4390178, WKetel commented:

"The potential for problems with NTSC video always comes back to cost. Saving half a cent but reducing the resolution 15% is OK if it cuts the cost.

"The result was that a whole lot of the video stuff produced was indeed junk, adding to the impetus to switch over to digital video. Nobody really complained about the poor picture quality, because that was what they had been taught to expect. It used to be better, though.

"The big benefit of digital, in obsoleting all of the analog sets, [was in] opening a whole new market. The next step will be some digital encoding, resulting in pay per view for everything.

"Not just yet, but give it another year or two."

EDN invites all of its readers to constructively and creatively comment on our content. You'll find the opportunity to do so at the bottom of each article and blog post.

### SLIDESHOW: AFTER THE MARS ROVER—A MINING **COLONY IN 2039**

NASA's most advanced Mars rover, Curiosity, has landed on the Red Planet. The one-ton rover, hanging by ropes from a rocket backpack, touched down on Mars to end a 36-week flight and begin a twoyear investigation. What's next? President Obama has laid out a bold vision for sending humans to Mars in the mid-2030s.

www.edn.com/4391812

### WHITE LEDS PRINTED ON PAPER: A DOCTORAL **THESIS**

Here is a doctoral thesis. provided as a multipart article, demonstrating that white LEDs made from zinc oxide and a conducting polymer can be manufactured directly on paper.

center of the engineering universe

### **ENGINEERING COMMUNITY**

**Opportunities to get involved and show your smarts**

### **DESIGN EAST**

Will embedded programming be dead by 2030? Which disruptive technologies and consumer innovations are on the verge of hitting critical mass? What's the latest in Android, LEDs, and sensors? Explore the hottest developments in engineering, build knowledge and skills, network with peers and technical experts, discover cutting-edge products and technologies, and find solutions to your biggest design challenges at

Design East, September 17 to 20 at the Hynes Convention Center in Boston: http://east.ubmdesign.com.

AUGUST 2012 | EDN 9 [www.edn.com]

EDN.COMMENT

### BY PATRICK MANNION, BRAND DIRECTOR

### Next-gen "Edisons" doing just fine

he notion that engineering's best and brightest are falling back on iPhone and Android apps instead of doing "real" engineering was put to rest in Austin this month at NIWeek's Graphical Systems Design Achievement Awards. I saw this fallacy for what it was as I prepared to announce that Peritec Inc's Naoki Hoshino had won the Editor's Choice honor for his work on a desktop EMI evaluation system.

We've seen the footage from revered colleges, such as Stanford, showing dorm rooms packed with the next generation of engineers seemingly focused more on smartphone apps than on the next tech breakthrough. We've heard OEMs complain that engineers are coming out of college ill prepared for the engineering world. It's easy to despair over what those signs might mean for the future of the tech industry.

But when I attend an event like the NIWeek GSDA awards (which EDN parent UBM Electronics co-sponsored), I emerge reinvigorated and brimming with optimism. I meet young innovators who are wrestling with real-world problems, from clinical assessment of conditions such as osteoporosis using ultrasound and lasers to off-grid energy solutions and earthquake monitoring.

The event's engaging master of ceremonies, Dave Wilson, director of academic and training and certification marketing for National Instruments, kept the proceedings moving as he deftly described every paper. What resonated with me most, however, were his

### JOIN THE CONVERSATION

closing remarks on technical audaciousness and sheer ingenuity.

For some in the *EDN* community, a design based on LabView combined with a modular PXI or CompactDAQ box may not epitomize "true" design. But I really liked what James Truchard, NI's cofounder, president, and CEO, had to say during his keynote address the day

Hoshino shows off his project on the show floor. Turns out he's a regular guy—a really smart one.

before the GSDA event: "Our goal is to make all these Edisons make progress."

I wonder what Thomas Edison himself would have done with LabView, NI hardware, and some Xilinx FPGAs. The possibilities boggle the mind.

For his part, Editor's Choice honoree Hoshino's paper was on "Developing an EMI desktop evaluation system using a new measurement technique" (http://bit.ly/P4xOoK). I chose it as the winner because the problem was technically challenging; because the work has long-term implications; and, in the spirit of the awards, because the achievement itself democratizes innovation by greatly reducing the cost of evaluating a design for EMI by eliminating the need to buy

Naoki Hoshino of Peritec accepts Patrick Mannion's congratulations on his Editor's Choice honor at NIWeek's Graphical Systems Design Achievement Awards.

or rent space at an anechoic chamber.

Of course, the work of stellar performers such as Hoshino and the GSDA winners won't quell the calls for "better" education or "more qualified" engineers, but what do such terms even mean anymore? Engineering has changed on many levels, and the emerging generation of engineers reflects those changes. Sometimes, as in Hoshino's case, the innovators themselves change the way engineering is done. The one constant: The work is about solving problems.

I'm curious to know how newer engineers and their more experienced counterparts truly view each other across the generational divide. I'd define a "new engineer" as one who has been out of college for 10 years or less. What do you think?EDN

Contact me at patrick.mannion@ubm.com.

Here's the full EMI measurement system in operation. On the left is the PXI box with LabView running on top. To the right, the EMI probe measures the EMI directly over an IC.

## **EDN**

### **BRAND DIRECTOR**

Patrick Mannion 1-631-543-0445; patrick.mannion@ubm.com

### **EXECUTIVE EDITOR**

Rich Pell Consumer 1-516-474-9568; rich.pell@ubm.com

### **MANAGING EDITOR**

Amy Norcross

Contributed technical articles

1-781-734-8970;

amv.norcross@ubm.com

### MANAGING EDITOR, ONLINE

Suzanne Deffree

DIY, STEM, Industry Watch

1-631-266-3433;

suzanne deffree@uhm.com

### SENIOR TECHNICAL EDITOR

Steve Taranovich

Analog, Power, Design Ideas

1-631-413-1834;

steve.taranovich@ubm.com

### **CONTRIBUTING EDITOR**

Carolyn Mathas LEDs, Communications 1-530-873-3755; cmathas@earthlink.net

### CONTRIBUTING EDITOR

Stephen Evanczuk Systems Design 1-802-549-4644; sevanczuk@gmail.com

### DESIGN IDEAS CONTRIBUTING EDITOR

Glen Chenier edndesignideas@ubm.com

### ASSOCIATE EDITOR

Diana Scheben 1-631-983-7693; diana.scheben@ubm.com

### **ASSOCIATE EDITOR**

Jessica MacNeil 1-212-600-3243; jessica.macneil@ubm.com

### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Brian Bailey, brian\_bailey@acm.org Robert Cravotta robert.cravotta@embeddedinsights.com

### VICE PRESIDENT/DESIGN DIRECTOR

Gene Fedele

### **CREATIVE DIRECTOR**

David Nicastro

### ART DIRECTOR

Giulia Fini-Gulotta

### PRODUCTION

Adeline Cannone, Production Manager Laura Alvino, Production Artist Yoshihide Hohokabe, Production Artist Diane Malone, Production Artist

### EDN EUROPE

Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

### EDN ASIA

Huang Hua,

Operations General Manager

huang.hua@ednasia.com

Grace Wu,

Associate Publisher

grace.wu@ednasia.com

Vivek Nanda, Executive Editor

vnanda@alobalsources.com

### **EDN CHINA**

Huang Hua,

Operations General Manager

huang.hua@ednchina.com

Grace Wu,

Associate Publisher

grace.wu@ednasia.com

grace.wu@ednasia.com Jeff Lu, Executive Editor jeff.lu@ednchina.com

### EDN JAPAN

Masaya Ishida, Publisher mishida@mx.itmedia.co.jp Makoto Nishisaka, Editor mnishisa@mx.itmedia.co.jp

### UBM ELECTRONICS MANAGEMENT TEAM

Paul Miller,

Chief Executive Officer, UBM Technology

Kathy Astromoff,

Chief Executive Officer, UBM Electronics

Brent Pearson,

Chief Information Officer David Blaza, Senior Vice President

Senior Vice President

Karen Field,

Senior Vice President, Content

Jean-Marie Enjuto,

Vice President, Finance

Barbara Couchois

Vice President, Partner Services and Operations Felicia Hamerman,

Vice President, Marketing Amandeep Sandhu,

Amandeep Sandhu,

Director of Audience Engagement

and Analytics

For a complete list of editorial contacts, see http://ubmelectronics.com/editorial-contacts

# MAXIMUM SELECTION OF PCB PINS& RECEPTACLES

# OVER 800 STYLES AND OPTIONS IN STOCK

Suitable for applications subject to high amounts of vibration and shock, Mill-Max pins and receptacles are available in diameters from .008" (.20mm) to .250"

(6.35mm). Receptacles feature a 4 or 6 finger beryllium copper or beryllium nickel contact to ensure integrity of connection for use in the harshest environments.

Don't see what you need? Rapid prototyping and custom designs are our specialty.

www.mill-max.com/EDN621

# INNOVATIONS & INNOVATORS

### LED increases efficacy by 20%

ree Inc's new XLamp XP-G2 high-brightness LED produces up to 20% more lumens per watt and 2.5 times the lumens per dollar compared with the company's original XP-G LED. The brighter, more efficient XP-G2 LED provides customers with an immediate boost in performance and lets luminaire manufacturers either use fewer LEDs to get the same brightness at lower cost or increase brightness levels using the same LED count and power.

Characterized and binned at 85°C, the XP-G2 LED leverages the same 3.45×3.45-mm footprint as the XP-G LED and is compatible optically with the original part, providing drop-in-ready performance enhancements to shorten the LED-fixture design cycle and improve customer time to market. The LED can enable a broad range of high-lumen applications, from indoor and outdoor installations to portable and lamp retrofits.

Built on Cree's new SC³ technology platform, XP-G2 LEDs combine high light output, reliability, and efficacy to deliver up to 151 lumens/W at 350 mA, 85°C or 165 lumens/W at 350 mA, 25°C in cool white (6000K). In warm white (3000K), the XP-G2 LED delivers up to 133 lumens/W at 350 mA, 85°C or 145 lumens/W at 350 mA, 25°C. The silicon-car-

bide-based SC³

technology platform

features advancements

in LED chip architecture and

phosphor formulation, as well as a

new package design.

Luminaire makers seeking Energy Star qualification will have access to specification and performance data, including LM-80 reports, which can speed time to market. XP-G2 LEDs are a "successor" product to the original XP-G LED for LM-80 data; that status accelerates the qualification of luminaires using just 3000 hours of LM-80 data instead of the normal 6000 hours.

The ROHS- and REACH-compliant XP-G2 LED features a maximum drive current of 1.5A and a level 4 rating and is UL-recognized. Distributor Mouser lists the XP-G2 in cool white at \$5.18 in sample quantities.—by Margery Conner > Cree, www.cree.com.

The brighter, more efficient XP-G2

LED provides an immediate boost in

performance and enables manufacturers

to use fewer LEDs to get the same

brightness at lower cost or increase

brightness levels using

the same LED count

and power.

### **TALKBACK**

"The hardware engineers realized the ship was sinking fast and did what all smart rats do. Launching a product with obsolete components that was far behind deadline [was] not a good career move."

—Commenter DCH, in response to a Tales from the Cube entry, at www.edn.com/4390916. Add your own comment.

>> Find out how LabVIEW can make you better at ni.com/labview/better

800 453 6202

# pulse

### Terahertz scanner on your smartphone?

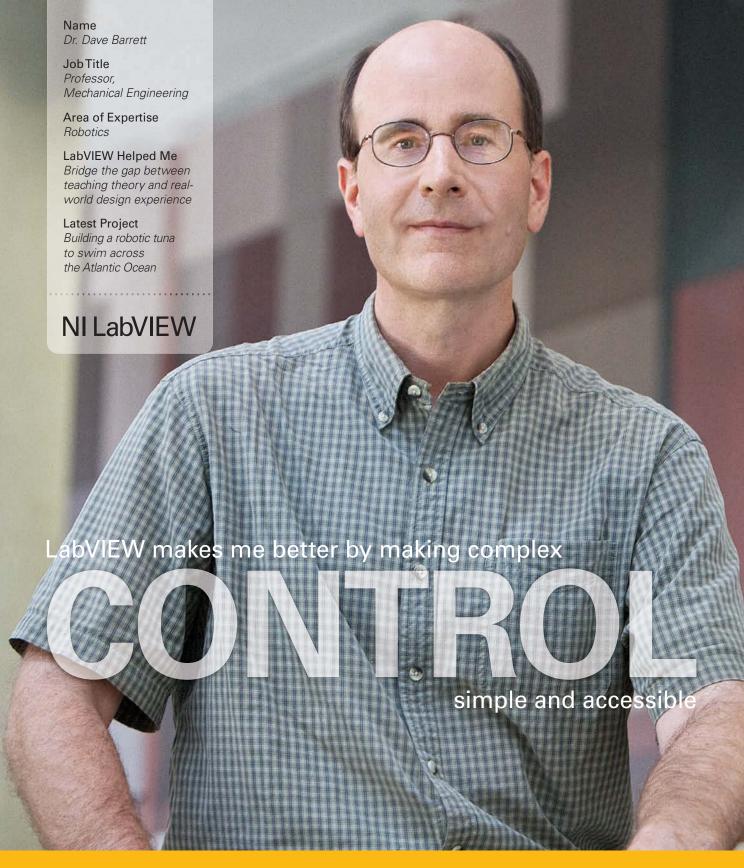

erahertz radiation—the portion of the electromagnetic spectrum between microwaves and infrared light—can penetrate fabric and just a few millimeters into the skin without the damaging effects of X-rays, promising safer gear for medical and security imaging. To date, however, generating terahertz radiation has required lasers, vacuum tubes, and special circuits cooled near absolute zero. often in room-sized apparatuses costing thousands of dollars. An experimental method for generating terahertz signals using familiar, inexpensive CMOS chip technology could one day put the same functionality in a handheld device.

narrow frequency band. Connect two springs and set one vibrating, and the other also will begin to vibrate; eventually they will settle to equilibrium. A ring of electronic oscillators does the same, and the circuits coupling the oscillators can set the frequency at which they will lock in.

In Afshari's device, the couplers also shift the phase of the signals—that is, how the peaks and valleys of the waves line up. With the right adjustment, the peaks and valleys cancel out each other at several harmonics but reinforce each other at the fourth harmonic, channeling most of the power there.

The Cornell team report-

This electron-microscope image shows the prototype chip, which uses a ring of coupled oscillators to generate terahertz radiation. The design focuses most of the energy in a high harmonic; the signal radiates on the axis of the ring and can be aimed (courtesy Ehsan Afshari).

Cornell researchers fabricated experimental chips that generated signals with about 10,000 times the power level previously obtained at terahertz frequencies on a silicon device.

Ehsan Afshari, assistant professor of electrical and computer engineering at Cornell University, came up with a tuning method that couples several oscillators in a ring to produce a high-quality signal, funneling the power into a very

edly fabricated experimental chips that generated signals with approximately 10,000 times the power level previously obtained at terahertz frequencies on a silicon chip. The Cornell researchers believe that by adjusting the couplers sepa-

rately, they might aim the output, making it possible to scan large areas with a narrow, highpowered beam.

A range of applications might harness terahertz radiation if the equipment cost could be contained. Terahertz scanners can identify skin cancers too small to see with the naked eye. Many of the complex organic chemicals used in explosives absorb terahertz radiation at particular frequencies, creating a "signature" that detectors can read. And because higher frequencies can carry more bandwidth, terahertz signals might yield a "super Bluetooth" mechanism for transferring a full-length high-definition movie wirelessly in seconds.

Afshari is working with Cornell colleagues to implement his method in gallium nitride, which can handle both higher frequencies and higher power. The focus, however, is on CMOS chips that could deliver sophisticated scanning in a smartphone form factor.

The National Science Foundation, the U.S. Office of Naval Research, and Semiconductor Research Corp funded Afshari's research.

−by Steve TaranovichCornell University,www.cornell.edu.

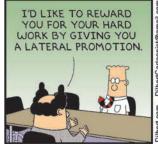

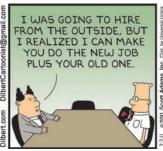

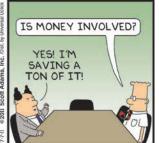

### DILBERT By Scott Adams

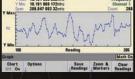

### It's more than a frequency counter. It's a high-speed answer tool.

Watch a 53200 Series video overview http://goo.gl/6CpGl

Agilent RF/universal frequency counters outperform in every way. Including a large color display for built-in analysis, up to 25x improvement in timing measurements, unparalleled connectivity, and a 100x increase in reading speed. All so you can accelerate your answers whether you're on the bench or manufacturing line.

### Agilent 53200 Series RF/Universal Frequency Counters

53210A 350 MHz, 10 digit/s, RF frequency counter

53220A 350 MHz, 12 digit/s, 100 ps, universal frequency

counter/timer

53230A 350 MHz, 12 digit/s, 20 ps, universal frequency

counter/timer with continuous/gap-free measurements

Agilent and our

Distributor Network

Right Instrument.

Right Expertise.

Delivered Right Now.

TESTEQUITY

800-732-3457 www.testequity.com/agilent See these high-speed answer tools in action View videos and download interactive brochure www.testequity.com/Agilent\_Counter

© Agilent Technologies, Inc. 2012

# pulse

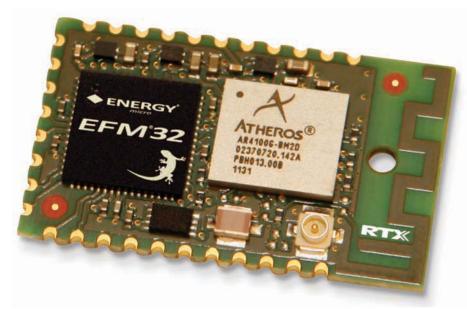

# Nordic offers BLE, ANT single-chip solutions

ordic Semiconductor has announced the first members of its nRF51 SOC family for 2.4-GHz applications. Based on the ARM Cortex-M0 core, the devices include the multiprotocol nRF51822, targeting proprietary and BLE (Bluetooth Low Energy) applications, and the nRF51422, which Nordic says is the industry's first SOC for the ANT/ANT+ wireless network protocol. An improved radio design and the high-performance 32-bit core at the heart of each device enabled Nordic to boost the radio link budget by 9.5 dB while cutting power requirements.

Designed for low-power coin-cell battery applications, the devices feature peak current of less than 10 mA and a fine-grained power-management scheme. A programmable peripheral-interconnect design enables autonomous operation of peripherals, reducing the power consumption associated with processor operations; in fact, Nordic heavily leveraged the speed and increased code density of the 32-bit ARM core to reduce power-hungry CPU cycles.

"The Cortex's 100× faster start-up time means less current is required for start-up, and 10× higher performance means it finishes processing faster, so the duty cycle is much improved," says Thomas Embla Bonnerud, director of product management at Nordic. "As a result, the devices require 50% lower average current compared with previous generations of Nordic RF ICs."

In providing BLE and ANT/ANT+ stacks on the separate devices, Nordic used a protected mem-

ory architecture that separates application code from stack code. Developers use APIs provided as header files in the company's software development kit. All application code interacts with the provided stacks through function calls, a methodology that Nordic expects will speed development and reduce the conflicts often found in development of wireless applications based on software stacks provided as libraries.

According to Bonnerud, this separation was essential for reliable application development on SOC devices. "Two-chip solutions are good because you don't have to worry about the stack, but when you have to manage stack code in your application, you end up with tons of dependencies," he says.

In providing BLE and ANT/ ANT+ stacks on the separate devices, Nordic used a protected memory architecture that separates application

code from stack code.

"For the nRF51, the application developer sees a standard stack; but because we use clean APIs, the code is runtime-protected, so the application code can't do anything that affects the stack."

Sampling now to customers, the devices will be generally available in early September, with production quantities scheduled for availability later in the year. According to Bonnerud, pricing will be approximately \$2, depending on quantity.

−by Stephen EvanczukNordic Semiconductor,www.nordicsemi.com.

# Printable conductive gel promises low-cost biosensors, energy storage

Stanford University researchers have reported on an electrically conductive hydrogel, synthesized from readily available organic material, that can be ink-jet printed and that demonstrates what researcher Yi Cui calls "remarkable electronic properties."

Polymer gels that feel and behave like biological tissue but are as electrically conductive as a metal or semiconductor hold promise for biosensor and energy-storage devices, but most of the gels developed to date are difficult to manufacture, and their conductive properties are limited. The Stanford team says its substance is inexpensive to make, and Cui states the gel's conductance is "among the best you can get" through the processes devised thus far.

Zhenan Bao, a chemical engineering associate professor, and Cui, a materials science and engineering associate professor, made the gel by binding long chains of the organic compound aniline together

with phytic acid. The acid, found naturally in plant tissue, can grab up to six polymer chains simultaneously to yield an extensively cross-linked network that forms a complex, sponge-like structure. Pores in the nanostructured hydrogel expand its surface area, increasing the amount of charge it can hold, the speed of its electrical response, and its sensitivity as a chemical sensor.

Stanford postdoctoral fellow Guihua Yu, associate professor Zhenan Bao, and visiting scholar Lijia Pan examine the hydrogel synthesized in Bao's lab (courtesy Linda A. Cicero, Stanford News Service).

"There are already commercially available conducting polymers, but they all form a uniform film, without any nanostructures," says Bao.

The material doesn't solidify until the last synthesis step, so it can be printed or sprayed as a liquid that gels once it's in place, opening the door to low-cost manufacture of intricately patterned electrodes. "You can't print Jell-O," says Cui. "But with this technique, we can print it and make it Jell-O later."

Most hydrogels are tied together by a large number of insulating molecules, reducing their ability to pass electrical current, but because phytic acid is a small-molecule dopant, the Stanford-developed gel is highly conductive. The substance's similarity to biological tissue, large surface area, and electrical capabilities suit it for application in biological systems that communicate with hardware, according to the researchers.

Stanford's Precourt Institute for Energy funded the research.

-by Diana Scheben

Stanford University,

www.stanford.edu.

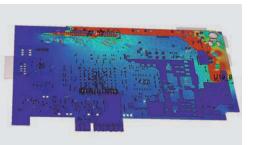

# Making Sense of the Real World – System Level EM Simulation

IR-drop: surface current density distribution on multilayer PCB

Components don't exist in electromagnetic isolation. They influence their neighbors' performance. They are affected by the enclosure or structure around them. They are susceptible to outside influences. With System Assembly and Modeling, CST STUDIO SUITE 2012 helps optimize component as well as system performance.

Involved in signal or power integrity analysis? You can read about how CST technology was used to simulate and optimize a digital multilayer PCB's performance at www.cst.com/pcb.

If you're more interested in EMC/EMI or microwave components, we've a wide variety of worked application examples live on our website at www.cst.com/apps.

Get the big picture of what's really going on. Ensure your product and components perform in the toughest of environments.

Choose CST STUDIO SUITE 2012 – complete technology for 3D EM.

CHANGING THE STANDARDS

# pulse

### **VOICES**

### Finally, a hardware accelerator: Bolt's Ben Einstein on a leg up for hardware start-ups

xperienced product designer and entrepreneur Ben Einstein is part of a team in Boston looking to give hardware start-ups their fair share of the glory. Bolt (http://buildatbolt.com), a new accelerator program that Einstein cofounded, aims to be a tool kit for hardware start-ups rather than for software and Webservices companies—popular draws for talent and investment that in the current environment have more support at their disposal. Einstein recently spoke to *EDN* about what Bolt is, what types of young companies it is looking for, and why the focus is on hardware. Read on for excerpts of the conversation, and get more of Einstein's thoughts at www.edn.com/4392154.

### Tell us what Bolt is all about.

We focus on the startup community. We're basically an accelerator program designed to help hardware companies. The general premise is that if you are building a software company, there are so many resources available that are incredibly useful-software review, mentoring programs—and raising money is often fairly easy because there is so much awareness and popularity in the space. Bolt is explicitly built from the ground up to do similar things, but for hardware companies.

We have prototyping facilities and a full-time engineering staff; we help people go to Asia for manufacturing and tooling; we know how to talk to buyers. We have an open application process; anyone from anywhere in the world can apply. We will accept between 10 and 12 teams every six months and give them a little seed capital to help keep them alive.

# Why focus on physical products as opposed to software or an app?

There are maybe 150 [support programs] for software in the US [alone]. And there's this device phenomenon that is about to explode. [The targeted] companies act like software companies in terms of their revenue structure, the kinds of founders they attract, the way the IP is locked up, but they tend to have a piece of hardware that is sort of a barrier to entry.

There's a phrase that is thrown around, "software wrapped in plastic," which is what some of these companies begin to look like. They have a relatively simple piece of hardware, but it ends up enabling a new set of functionality and user applications [so that they] work like software companies; they have reocurring revenue streams, multiple products around one piece of hardware, and reoccurring interactions with customers.

There's also [the fact that] these hardware companies aren't being helped at all. It's very difficult for some of these young companies to get the tools and systems they need to get to market, whereas in the app world a lot of that is pretty easy to come by. We are trying to leverage that.

### What are you looking for?

Great teams, but we are really looking for great people. The [online] application is tailored to find teams of great people. It's really simple; it's not designed to be a business plan.

When it comes to prototyping, what can an entrepreneurial engineer learn from a company like Dyson or iRobot or other former startups that showed distinct, difficult, or maybe risky designs in their beginnings?

Bolt is based on building markets and helping people find their way along the path of building a product. It's less about the sexy, sleek prototype that people are really attracted to. The MVPminimum viable productapproach involves doing as little as possible to prove that somebody really likes what you are doing. It's part of the lean start-up movement ... and involves growing the company around a core group of users and satisfying that need.

We take a similar approach when building products.

When people think about start-ups, they think about twenty-somethings just out of school. Do you see opportunities for more experienced engineers?

We expect a good portion of our applicants to be in that [younger] category. But the other category is the frustrated engineers who are at a company like Apple or Motorola and have sort of been in their middle position and chugging along but feel that they want to be more creative and try out their own concept. Those [engineers] are really attractive to us. The only trick is that we are not providing enough capital to provide for families when the business is getting started. They have to be able to basically survive on their own for six months or so.

We expect that a smaller pool of the applicants would be these kinds of guys, but we encourage them to apply. You have to have a certain kind of crazy to start a company, especially in hardware, and that tends to be beaten out of people as they get older. But their experience [can be] incredibly valuable. Even if they are not leading the charge, it's great to have them on a team with two or three younger guys. - interview conducted and edited by Suzanne Deffree

Einstein will be presenting at next month's Design East conference, hosted by UBM. Register and get more information at http://east.ubmdesign.com.

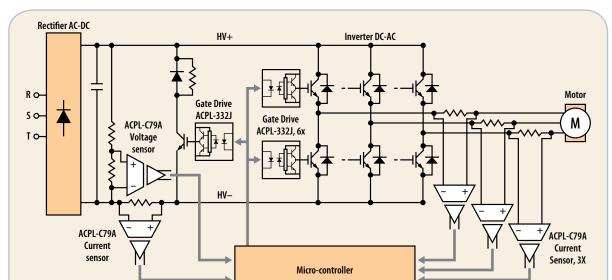

### The Avago Advantage

# Protecting IGBTs with Avago Optical Isolation Amplifiers

### Introduction

Insulated-gate bipolar transistors (IGBTs) can fail when subjected to overloads and overvoltages. Isolation amplfiers (iso-amps) can respond quickly to over-current and overload conditions when used on the output phases and the DC bus.

A typical block diagram of a power converter in an AC motor drivet consists of an inverter that converts the DC bus voltage to AC power at a variable frequency to drive the motor. IGBTs are expensive power switches that form the heart of the inverter. These power devices must operate at a high frequency and must be able to withstand high voltages.

Iso-amps such as the ACPL-C79A work with shunt resistors to accurately measure power converter current even in the presence of high switching noise. When used with a resistive divider, iso-amps work as precision voltage sensors to monitor the DC bus voltage. The microcontroller monitors the current and voltage information from the iso-amps and uses the data to calculate the feedback values and output signals needed to for fault management in the IGBTs and power converters.

### **Fault Protection**

However, the IGBT protection must be such that its cost doesn't affect that of the motor drive system. IGBT gate drivers such as the ACPL-332J and current sensors with protection features can detect faults economically in this regard. They eliminate the need for separate detection and feedback components.

Over-current conditions in an IGBT can arise from a phase-tophase short, a ground short or a shoot through. The shunt + iso-amp devices on the output phases and DC bus can, besides measuring current, detect such faults.

Typical IGBT short-circuit survival times are rated up to 10  $\mu$ sec. So any protection must prevent this limit from being exceeded. Within 10  $\mu$ sec, the circuit must detect the fault, notify the controller and complete the shutdown. Iso-amps use various methods to get these results.

For instance, the ACPL-C79A has a fast, 1.6 µsec response for a step input. That lets the iso-amp capture transients during short-circuits and overloads. The signal propagation delay from input to output at mid point is only 2 µsec, while it takes just 2.6 µsec for the output signal to catch up with input, reaching 90% of the final levels.

Another example is the HCPL-788J, which responds quickly to over-currents using a different approach. In addition to the signal output pin, it has a Fault pin that toggles quickly from High to Low level when over-current occurs. This iso-amp provides ±3% measurement accuracy.

In the fault feedback design, nuisance tripping can be an issue. This is a triggering of fault detection in the absence of any damaging fault condition. To avoid false triggering, the HCPL-788J employs a pulse discriminator that blanks out di/dt and dv/dt glitches. The advantage of this method is that

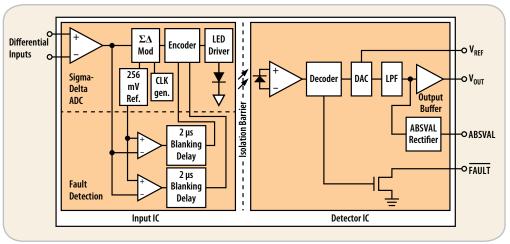

Figure 1: Block diagram of power converter in a motor drive

Figure 2: In the HCPL-788J iso-amp, the differential input voltage is digitally encoded by a sigmadelta A/D converter and then fed to the LED driver, which sends the data across the isolation barrier to a detector and D/A.

rejection is independent of amplitude, so the fault threshold can be set to low level without risking nuisance tripping.

The circuit that detects faults quickly contains two comparators in the Fault Detection block to detect the negative and positive fault thresholds. The switching threshold is equal to the sigma-delta modulator reference of 256 mV. The outputs of these comparators connect to blanking filters with a blanking period of 2  $\mu$ sec and then go to the Encoder block.

To ensure speedy transmission of the fault status across the isolation boundary, two unique digital coding sequences represent the fault condition, one code for negative, the other for affirmative. Detection of a fault interrupts the normal data transfer through the optical channel and replaces the bit stream with the fault code. These two fault codes deviate significantly from the normal coding scheme, so the decoder on the detector side immediately recognizes the codes as a fault conditions.

The decoder needs about 1 µsec to detect and communicate the fault condition across the isolation boundary. The anti-aliasing filter adds a 400 nsec delay to give a propagation delay of 1.4 µsec. The delay between the fault event and the output fault signal is the sum of the propagation delay and the blanking period (2 µsec) for an overall 3.4 µsec fault detection time.

The Fault output pin allows fault signals from several devices to be wire-ORed together forming a single fault signal. This signal may then be used to directly disable the PWM inputs through the controller.

### Overload Detection

An overload condition refers to a situation where the motor current exceeds the rated drive current, but without imminent danger of failure, as when the motor is mechanically overloaded or is stalling because of a bearing failure

Inverters usually have an overload rating. The time period of the allowable overload rating depends on the time it takes before overheating becomes an issue. A typical overload rating is 150% of nominal load for up to one minute.

The ACPL-C79A accepts full-scale input range of  $\pm 300$  mV and the data sheet specifications are based on  $\pm 200$  mV nominal input range. Designers can choose the overload threshold at or in between either of the two figures. Usually the measurement accuracy of the overload current is less stringent than that of the normal operating current. Here, setting the threshold near 300 mV is a good choice. This allows full use of the iso-amp's dynamic input range. However, a threshold set at 200 mV ensures accurate measurement of the overload current. Once the voltage levels are decided, the designer must choose appropriate sense-resistor value according to corresponding current level.

The HCPL-788J includes an additional feature, the ABSVAL output, which can be used to simplify the overload detection circuit. The ABSVAL circuit rectifies the output signal, providing an output proportional to the absolute level of the input signal. This output is also wire OR-able. When three sinusoidal motor phases are combined, the rectified output (ABSVAL) is essentially a DC signal representing the RMS motor current. This DC signal and a threshold comparator can indicate motor overloads before they can damage to the motor or drive.

### **Overvoltage Detection**

The DC bus voltage must also be continuously controled. Under certain operating conditions, a motor can act as a generator, delivering a high voltage back into the DC bus through the inverter power devices and/or recovery diodes. This high voltage adds to the DC bus voltage and puts a very high surge on the IGBTs. That surge may exceed the maximum IGBT collectemitter voltage and damage them.

The miniature iso-amp (ACPL-C79A) is often used as a voltage sensor in DC bus monitoring applications. A designer must scale down the DC bus voltage to fit the input range of the iso-amp by choosing R1 and R2 values to get an appropriate ratio.

## Now Enhanced & Interactive

EXPERT CONTENT | DESIGN CENTERS | TOOLS & LEARNING | COMMUNITY

You turn to us for the resources, ideas, & solutions you trust. Now get even more with the new **EDN.com**.

### BY BONNIE BAKER

# Instrumentation amplifier input-circuit strategies

any industrial and medical applications use instrumentation amplifiers to condition small signals in the presence of large common-mode voltages. INAs have complete closed-loop operational amplifiers with feedback components included. Under normal conditions, an INA is easy to use, as long as you pay attention to the input stage and the output of the first stage. The quick and inexpensive solutions described here can help you avoid the INA circuit's input-stage pitfalls.

In a classic, three-op-amp INA (Figure 1), the input stage has two op amps in an adjustable-gain configuration and provides high input impedance on both the inverting ( $V_{\rm IN}$ ) and noninverting ( $V_{\rm IN}$ ) inputs. The output stage has four matched resistors around a single op amp. When the circuit designer exercises proper precautions with the input pins, this configuration rejects external common-mode voltage and noise. The output stage has a reference voltage that level-shifts the output with respect to

ground. The level shift is convenient in single-supply applications. As with many INAs, you can program the gain found in **Figure 1** with a single resistor,  $R_{\rm G}$ .

Depending on the INA's silicon process,  $V_{\rm IN+}$  and  $V_{\rm IN-}$  connect to a bipolar transistor base, FET gate, or CMOS gate. All inputs to the INA require a current-return path to ground and a bias-voltage reference. Without the current-return path and the bias-voltage reference, the INA input stage saturates or floats to an undesirable voltage. Either condition

$V_{\text{IN}}$   $V_{\text$

Figure 1 In a classic, three-op-amp INA topology with input sources that define  $V_{CM}$  and  $V_{D}$ , the input stage has two op amps in an adjustable-gain configuration and provides high input impedance on both  $V_{IN-}$  and  $V_{IN+}$ .

creates an invalid output voltage.

The floating thermocouple circuit in Figure 2a, available online at www. edn.com/4392026, does not provide a current path to ground or a bias-voltage reference for the INA's input pins. Thus, the input-current leakages are not dissipated, and the two inputs can float to any undefined voltage. That situation, in turn, causes the INA's output to change to an invalid output voltage, usually in the middle of the INA's output range. The invalid voltage can appear to be legitimate, making it difficult to detect the correctness of the INA input implementation. Figure 2b illustrates a correct thermocouple connection to an INA; both inputs have a path to ground—in this case, through a 10-k $\Omega$ resistor, biased to a voltage within the INA's input range, or ground.

Circuit designers often misapply a thermocouple or even a two-wire microphone to the INA's input circuit; the problem arises when the INA inputs are connected without proper consideration to current paths or biasing. Heed those considerations for the INA's input stage, and you can be confident that the INA's output voltage is representative of the thermocouple's voltage.

But wait—there may be a problem with the output values of A<sub>1</sub> and A<sub>2</sub> (**Figure 1**). How would *you* solve this problem? Comment online at www. edn.com/4392026. I'd really like to hear from you! **EDN**

### REFERENCES

- Kugelstadt, Thomas, "Getting the most out of your instrumentation amplifier design," *Analog Applications Journal*, Texas Instruments, 4Q 2005, http://bit.ly/Peilok.

- Trump, Bruce, "Instrumentation amplifiers—avoiding a common pitfall," TI E2E Community, March 27, 2012, http://bit.ly/Nw4er2.

- Trump, Bruce, "Instrumentation amplifiers—they're not op amps but what are they?" TI E2E Community, April 2, 2012, http://bit.ly/NCsxHI.

Bonnie Baker is a senior applications engineer at Texas Instruments.

# **VectorStar® Network Analyzers are technologically and economically smart.**

Anritsu's industry-leading technology delivers performance where it really matters. The VectorStar 70 kHz to 125 GHz flagship broadband system provides industry-best performance in all three critical performance areas: broadband frequency coverage, dynamic range, and measurement stability. Whatever your starting requirement, feel safe in the knowledge that Anritsu VectorStar offers the expandability you need in the future. As your needs grow, so can your VectorStar, with:

- 20, 40, 50, and 70 GHz models and the flagship 70 kHz to 125 GHz broadband system

- Industry-leading combination of frequency coverage, dynamic range, and stability

- Two-port, four-port, and multiport (4-12) variants

- Nonlinear measurement systems

For applications ranging from microwave component testing to on-wafer device characterization, when you want best-in-class performance and industry-leading technology, you know the answer—Anritsu.

To learn more and download an application note from our library, visit us at:

www.anritsu-offer.com/vna-edn/

Scan code for library:

### Microwave Bench Portfolio

40 kHz to 125 GHz VNA

- On-wafer and bench top

- Extensions to 750 GHz

Two-Port and Multiport VNA Solutions

• 20, 40, 50, and 70 GHz

### Signal Generators

- 0.1 Hz to 70 GHz

- Extensions to 325 GHz

- Low phase noise

Power Meters

- 10 MHz to 50 GHz USB Power Sensors

- 10 MHz to 26 GHz

# Volt's battery-stack manager aids

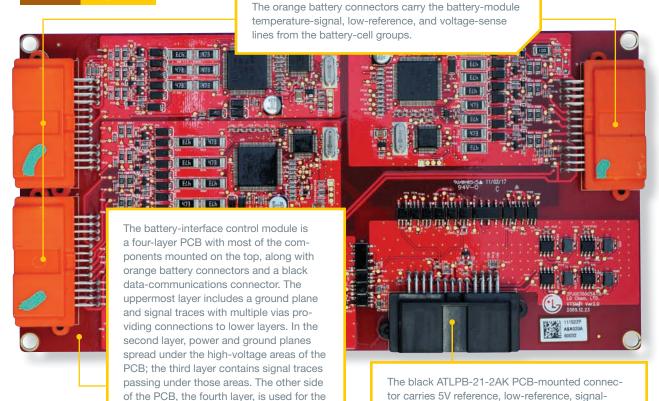

sophisticated battery-management system at the heart of the Chevrolet Volt ensures the safety and reliability of the multicell lithium-ion battery stack that delivers power on demand to the Volt drive system. Within the management system, battery-monitoring boards use two key subsystems to monitor cell health and deliver digital results to a host processor that orchestrates system operation. Separating those subsystems, a signal interface ensures isolation between high-voltage battery-sensing circuitry and communications devices on the boards.

At a given temperature and output current level, Li-ion cells maintain a nearly flat voltage output across the middle of their capacity range—a characteristic that heightens Li-ion's advantages as a power source but complicates engineers' attempts

to use simple cell-voltage measurements to provide users with a measure of remaining battery capacity, or SOC (state of charge).

For Volt drivers, an accurate SOC measurement is important for estimating vehicle range. Maintaining SOC within a specific range is also important for ensuring extended battery life; batteries kept at too low or too high a state of charge tend to degrade faster than those kept at intermediate levels.

In the Volt, GM engineers established a safe SOC window of 58% to 65%, depending on driving mode, with a lower limit in normal driving mode set to a 30% SOC and a higher, "mountain driving" mode limit set to 45%. When the Volt reaches the appropriate lower SOC limit, the vehicle's gasoline engine engages for extended-range operation. The battery-interface control-module boards provide the data needed to ensure a reliable SOC for Volt operation.

# Chevy's drive for safe power

181 kg, the battery stack generates the 16-kWh power needed to turn drive motors, power passenger features, and supply power to a battery-management system that rivals avionic systems in its complexity. As described by analysts at UBM TechInsights and Munro & Associates, the full Chevy Volt battery pack comprises 288 prismatic Li-ion cells, which are in turn packaged into 96 battery-cell groups to

Measuring 1.8m long and weighing

The battery-cell groups are combined with temperature sensors and cooling elements into four main battery modules. Voltagesense lines attached to each cell group terminate in a connector on top of each battery module, where a voltage-sense harness joins the connector to a battery-interface control module.

**WANT MORE?**

+ Find the full teardown, including video discussions with Avago Technologies product-marketing engineer Andy Poh on the role of isolation in the Chevy Volt battery-management system, at www. edn.com/4391497.

+ For a deeper look inside the Chevrolet Volt, including additional teardowns, visit www.driveforinnovation.com, sponsored by Avnet Express.

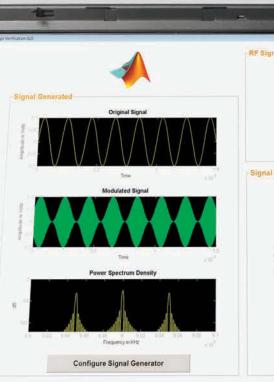

# CONNECT MATLAB TO YOUR TEST HARDWARE

with INSTRUMENT CONTROL and DATA ACQUISITION TOOLBOXES

Connect your test equipment directly to MATLAB using standard communication protocols and instrument drivers that support thousands of instruments. You'll be able to analyze and visualize your results as you collect them, using the full power of MATLAB.

MATLAB® SIMULINK® Hardware Support includes Agilent, Tektronix, LeCroy, Rohde & Schwarz, National Instruments, Anritsu, Keithley, Yokogawa, Tabor, Pickering, and more

Protocols and Standards supported include GPIB, LXI, IVI, PXI, AXIe, TCP/IP, VISA, USB, UDP, and RS-232

Find it at mathworks.com/connect supported hardware list

trial request

MATLAB is a registered trademark of The MathWorks, Inc. Other product or brand names may be trademarks or registered trademarks of their respective holders.

©2012 The MathWorks, Inc.

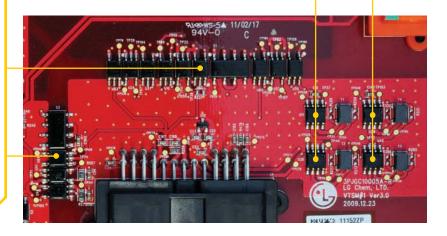

### TEAR DOWN

The heart of the battery-interface control system is a sophisticated sensing subsystem-a complete embedded system for monitoring the batterypack temperature and the voltage output from each Li-ion cell group. Each sensing subsystem pairs an L9763 ASIC, developed by STMicroelectronics and LG Chem, with a Freescale S9S08D732 40-MHz HCS08 microcontroller packing internal 32-kbvte flash, 2-kbyte RAM, and 1-kbyte E2PROM. An external, 4-MHz oscillator provides a reference frequency for microcontroller clock operations.

ground plane and signal traces and con-

tains some additional components.

Cell voltage passes through the battery connector to the L9763. The ASIC can monitor up to 10 individual Li-ion cell groups, using on-chip current-sense amplifiers for cell-load-current monitoring and an on-chip analog multiplexer and sample-and-hold circuit for cell-voltage monitoring. The part's differential inputs address the need to ensure millivolts-accurate measurements despite large offset voltages, depending on the cell's location in the battery pack. PCB designers used trace-layout techniques, isolation techniques, and the ground planes mentioned earlier to ensure signal integrity.

The S9S08DZ32 receives measurement data from the L9763 ASIC, which passes measurement data for its monitored Li-ion cells through its SPI interface to the microcontroller. The ASIC also provides a 5V LDO output for the microcontroller. For overall battery management. individual L9763 ASICs are linked through onchip interfaces, and the primary control unit addresses them individually through vertical daisy-chain communication.

ground, CAN bus high-serial-data, CAN bus low-

serial-data, and high-voltage-fault signals.

# The choice for

Get something extra for your solar inverter: a perfect fit! Our broad line of EPCOS power line chokes and our ability to modify means you get the right choke for your design. EPCOS brand power line chokes cover inductance values from 0.2 to 100 mH and offer high current capability — up to 54 A with double power line chokes and up to 62 A with triple power line chokes!

We offer chokes for up to 1000 V and with resistance between 1.5 and 2800 m $\Omega$ . Rated voltage is 250 V AC for double and 690 V AC for triple variants. Designed for temperatures of 40 to 85  $^{\circ}$ C, they are available in vertical or horizontal versions.

Call 1-888-768-2673 or visit www.epcos.com/inductors

### TEAR DOWN

In the battery-interface-module PCB, Avago ACPL-M43T optocouplers sit on the edge of the communications section, isolating it from the highvoltage-sensing subsystems, which are further shielded by ground planes in deeper PCB layers. The isolation interface provides three individual M43T optocouplers for each of the three lines brought out from each sensing circuit—specifically, the Freescale S9S08DZ32 CAN Tx output pin, microcontroller CAN Rx input pin, and high-voltage fault signal from the microcontroller. Output from the microcontroller CAN Tx pin, for example, passes through a shielded signal layer in the PCB to reach the pin 1 anode of an M43T to energize the embedded LED, resulting in a change of state at pin 5 (V). The isolated signal then passes to the communications output stage of the battery-interface module.

Sitting at the end of the communications signal chain, the Infineon TLE6250G CAN transceiver is an AEC-qualified IC that provides CAN physical-layer signaling between the physical cable and CAN protocol handler-here, the S9S08DZ32 microcontroller (via optocoupler isolation). Rated for 1M-baud CAN transmission, the device handles the conversion between the CAN\_H and CAN\_L signals on the differential signal wire and the CAN dominant and recessive bits transmitted and received by the S9S08DZ32. The eight-pin TLE6250G includes Tx, Rx, V<sub>cc</sub>, GND, CAN\_H, and CAN\_L pins, as well as two mode-control pins: INH and RM. When the TLE6250G senses a change on the Rx pin from the CAN recessive state to CAN dominant state, the device switches CAN\_H high and CAN\_L low. This symmetrical change in state reduces electromagnetic interference.

Ringing RLGC Thermal Stripline Routing

### Signal Integrity — Dr. Howard Johnson

and his

### extraordinary Black Magic seminars...

Houston, TX

8-9 Oct. **High-Speed Digital Design**

10-11 Oct.

Adv. High-Speed Signal Propagation

Huntsville, AL

4-5 Oct.

**High-Speed Noise and Grounding**

### www.sigcon.com

For serious digital designers. Use Promo code: EDN12

Distributed

Factorized

Power Management

Innovation

Integration

Performance

Speed

Efficiency

Density

# More Flexibility

Vicor gives power system architects the flexibility to choose from modular, plug-and-play components, ranging from bricks to semiconductor-centric solutions with seamless integration across all power distribution architectures. From the wall plug to the point of load.

Don't let inflexible power products slow you down. Choose from limitless power options to speed your competitive advantage.

### Flexibility. Density. Efficiency.

Trust your product performance to Vicor

BRICK

vicorpower.com/rp/flexibility/edn

Flexible Module Power

Support

Expertise

Productivity

Reliability

Qualified

### BY PALLAB CHATTERJEE

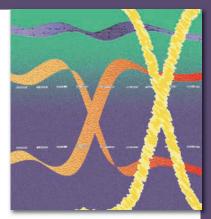

### In wireless, MIMO's the word

he fastest growing avenue of communications is via the wireless technologies that drive cellular communications, Wi-Fi, wireless display interfaces, and the large number of machines in the Internet of Things. This explosive growth is not without technical challenges, the most stringent of which is spectrum allocation. The more available channels and frequencies there are, the higher the number of devices that can communicate at one time, and the greater the bandwidth available for each device.

One driver for increased bandwidth use is video traffic over Internet Protocol networks. Video currently claims 60% to 75% of the IP bandwidth for Internet traffic overall, and it accounts for upward of 80% of the traffic on home networks and in industrial-control applications (including surveillance-and vision-system traffic). This video data includes still images as well as streaming and multiframe content.

One change to support the growing volume of traffic has been an increase in the frequency bands available for wireless connections. Wireless spectrum initially resided in the 900-MHz band, expanded to the 1.2-GHz and 2.4-GHz bands, and has now landed in the 5-GHz band.

On the mainstream Wi-Fi side (802.11), the a/b/g protocols are situated in the 2.4-GHz band and feature single antennas with single data streams. The 802.11n protocol supports dual-band, 2.4-GHz and 5-GHz operation; more important, it implements MIMO (multiple-input/multiple-output) data streams. Not only does the higher frequency help, but allowing two streams via the dual-transceiver configuration eases the transfer of large data sets.

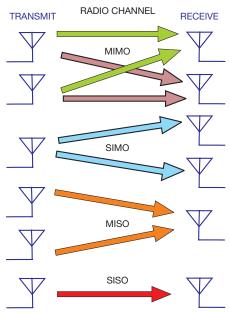

Figure 1 shows the progression in antenna techniques that have been used. The MIMO configuration for 802.11n was primarily seen in rout-

ers and gateways, rather than endpoints, in the first round of devices.

The concept was expanded and optimized for the new 802.11ac protocol, which allows for a four-channel MIMO configuration at a 5-GHz fixed frequency. Most ac-class routers will support the multiple-antenna set. A key change is that endpoint devices—tablets, smart-

Figure 1 Wireless-antenna configurations have progressed from single-input/single-output to multichannel MIMO.

phones, laptops, desktop devices, printers, and displays—can now support multiple antennas and multiple data streams. With the increased bandwidth from MIMO in the endpoint and router, high-definition and high-frame-rate video can now be transferred between devices without any QOE (quality of experience) lag or degradation.

Even as 802.11 Wi-Fi has shifted to a MIMO platform for new products, machine-to-machine protocols such as 802.15.4 under ZigBee and Z-Wave have done the same. The M2M protocols support dual configurations for the points in a mesh network. The dual transceivers typically function not as a pair to increase the effective transfer rate but as a simultaneous-send/receive pair. That setup enables video-data transfer through the mesh network to the final endpoint, while small data is transferred between points from the sensors that originated it.

Moving to a MIMO configuration involves other system changes for improved operation. For wireless systems, developers must coordinate the

data and signal flows through the multiple antennas in the product to improve performance.

The technique of beamforming can improve data transfer in the multiple-broadcast configuration. Beamforming adjusts the output-signal phase to compensate for the phase shift that occurs during the broadcast transmission. The technique ensures a high total signal level because the combined output signals do not cancel one another as a result of phase overlap.

Another major issue for a MIMO implementation is power. A setup that allows multiple antennas to be active at the same time requires separate RF blocks connected to the antennas. A four-channel system would require four power amplifiers and transceivers, with each capable of delivering the full power of the protocol set.EDN

Pallab Chatterjee has been an independent design consultant since 1985.

# THAT'S WHY THE WORLD'S AUTOMOTIVE COMPANIES COUNT ON TE CONNECTIVITY.

Soon, the ultimate connected device won't be in your pocket. It will be on the road. And TE Connectivity is making it possible, with connectivity solutions that drive today's most advanced hybrid and electric vehicles. We're helping automotive engineers develop safer, lighter, more robust ways to link power and data—from the Smart Grid to the charging station and throughout the vehicle. When the world needs a better way to get where it's going, we make every connection count. **EveryConnectionCounts.com**

**EVERY CONNECTION COUNTS**

**DesignNews**

EDN

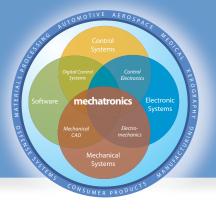

# MECHATRONICS FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEM AND SOFTWARE IN DESIGN

## "Mechatronify" common mechanisms

Through a combination of knowledge, process, and determination, even a Renaissance-era mechanism can be made mechatronic.

By Kevin C Craig, PhD

hat does it mean to "mechatronify" a mechanism or machine? It's more than just adding a sensor, actuator, and computer-control system; you must add them in an integrated way from the start of the design, using a model-based process that leverages analysis techniques and simulation software and that leads to optimal designs without trial and error. Combining old inventions with new technology fosters innovative ideas, but it is the process that transforms those ideas into reality.

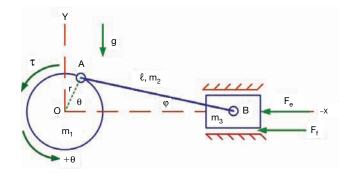

Consider a mechanism that Leonardo da Vinci developed more than 500 years ago and that now finds use in engines, automation applications, and miniature devices: the slider crank (**Figure 1**). The slider-crank mechanism comprises a flywheel crank, a connecting rod, and a slider, all assumed to be rigid. The external forces and torques acting on the mechanism are the servo-motor torque,  $\tau$ ; the slider friction force,  $F_t$ ; and the external force,  $F_c$ . In this special case of fourbar linkage, one crank is infinite in length, such that its end point (B) has rectilinear motion. It is a one-degree-of-freedom system; that is, only one coordinate is needed to describe its motion completely. The constraint **equation** relating angles  $\theta$  and  $\phi$  is  $r(\sin \theta) = \ell(\sin \phi)$ .

Graphical analysis of kinematics—the geometry of motion—can yield great insight. A mathematical solution, however, is more effective for mechatronic system design

and optimization, obtaining positions, velocities, and accelerations of key points, as well as the angular velocities and accelerations of the rigid bodies.

You can accomplish kinetic analysis by drawing free-body diagrams showing gravitational forces, contact forces/torques, and inertia forces/torques and then summing forces/moments as needed. This method, known as the

D'Alembert approach to applying Newton's Laws, can determine forces/torques at all joints. You can directly obtain the system **equation** of motion by applying Lagrange's Equation:

$$\frac{\mathrm{d}}{\mathrm{d}t}\frac{\partial T}{\partial \dot{\theta}} - \frac{\partial T}{\partial \theta} + \frac{\partial V}{\partial \theta} = Q_{\theta},$$

using the generalized coordinate  $\theta$ , where V is the system potential energy, T is the system kinetic energy, and  $Q_{\theta}$  is the generalized torque due to forces/torques that do work. The resulting equation has the form  $M(\theta)\ddot{\theta}+N(\theta,\dot{\theta})=F(\theta)$ .

Having completed the kinematic and kinetic analyses, you would next define the desired end-point trajectory and then compute the necessary motion profile for the actuator through inverse kinematics, which here would include the crank and connecting rod lengths. This step involves trajectory planning; you must define the profile in a way that avoids or reduces the mechanical vibration and stress on components and actuators while reducing overshoot response and excessive position error during motion. Electronic cams accomplish this task.

The inverse kinetic analysis, which includes masses, centerof-mass locations, and mass moments of inertia, is used to generate the required actuator torque/force for the motion profile, and results in a speed/torque-force diagram on which to base actuator selection. The chosen actuator now becomes part of the system; with that update, a control system—including

feedback, feedforward, and disturbance observer—can be designed, yielding a new speed/torque-force profile. You would then simulate the entire system, with the addition of any parasitic effects, for design validation.

Mechatronifying any mechanism requires sweating the details. But when you apply a combination of accumulated knowledge, process, and determination, innovation will happen. EDN

Figure 1 The slider-crank mechanism—a concept dating to da Vinci—comprises a flywheel crank, a connecting rod, and a slider.

e than 1,900 manufacturers • we stock nearly 4 billion componed to than 1,900 manufacturers • we stock nearly 4 billion componed to carry components from more than 1,900 manufacturers • that authorized lines we do it all we have a third-party to the buy direct from manufacturers • we offer excess purchasive supply chain management services • we stock nearly 4 billion that a global sourcing team • we have a component expined that 1,900 manufacturers • we have a third-party test for

E EUN CHECT NOM MANUTACTURERS . WE DEVE EUNDAZED IN

# One distributor meeting all your needs.

America II is the evolution of distribution.

America II's distribution model allows us to create a completely unique experience for our customers. We utilize an inventory-centric model in which we buy direct from approximately 400 manufacturers and stock nearly 4 billion components. In addition, our team of global commodity specialists sources components daily, while a team of inventory solutions experts offers asset recovery through excess purchasing programs. *The evolution of distribution is here.*

877.845.4393 www.americaii.com/edn

AMERICA II

ELECTRONICS Inc.

Quality, inventory, people. Making a difference.

# You make the connection. We provide the protection.

Protect your connectors, pins and leads from dust, moisture and impact damage with our full line of caps and plugs. Choose from hundreds of styles and sizes that are in-stock and ready to ship.

- Wide range of materials

- Certified to meet MIL/NAS specs

- Comprehensive custom capabilities

If we don't have it, we'll make it. We have a team of design engineers and in-house tool room dedicated to the development and production of custom parts to meet our customers' specific needs.

Visit us at www.caplugs.com or contact a technical sales specialist at I.888.CAPLUGS.

We've got everything covered.<sup>™</sup>

Caplings

# USING ANALOG BEHAVIORAL MODELS

BRINGING ANALOG AND MIXED-SIGNAL BLOCKS TO A HIGHER ABSTRACTION LEVEL YIELDS MORE EFFECTIVE MIXED-SIGNAL SIMULATION AND MORE COMPLETE VERIFICATION ENVIRONMENTS.

BY QI WANG . CADENCE DESIGN SYSTEMS

he era of "Internet everywhere" is creating a spectrum of applications targeted toward low-power and mixed-signal design, in segments ranging from health care to automotive to communications. Meanwhile, design challenges such as intellectual-property selection and integration as well as SOC- and system-level verification are spawning a whole new class of problems for EDA tools.

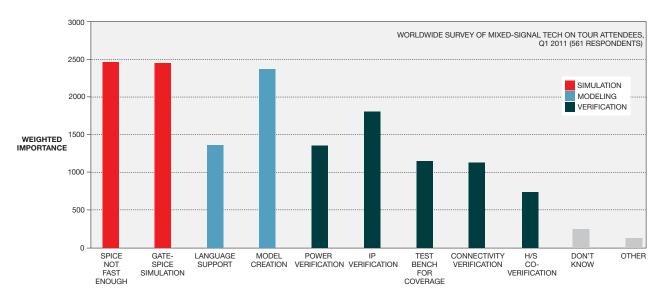

Mixed-signal design engineers face increasing difficulties in design and verification of complex mixed-signal SOCs. In a survey of mixed-signal design engineers during the 2011 Mixed-Signal Tech on Tour, a worldwide series presented by Cadence Design Systems Inc, the 561 respondents identified mixed-signal verification as a top customer challenge.

1AGE: ISTOCK

The performance of Spice simulation is prominent in the difficulties being reported (Figure 1). Analog Spice and Fast-Spice simulators are orders of magnitude slower than digital simulators and are slower still when compared with emulators and hardware accelerators. A June 2011 Design Automation Conference panel discussed the need for analog design and verification to become more like digital—that is, to become more structured and more top-down (Reference 1). Verification planning tools are required, and debug methodologies such as ABV (assertionbased verification), MDV (metric-driven verification), and UVM (universal verification methodology)-like selfchecking test benches must be created for analog/mixed-signal.

To tackle simulation-throughput issues, designers are turning to behavioral-modeling techniques, which can increase simulation speed. Such techniques include event-driven simulation based on Verilog-A, Verilog-AMS, and RNM (real-number modeling).

Analog behavioral models are typically written in Verilog-AMS, Verilog-A, VHDL-AMS, or SystemVerilog.

Verilog-A is a pure-analog subset of Verilog-AMS and is mainly used for detailed analog models for performance verification. The language is quite simple, but it is challenging to write a good behavioral model with Verilog-A that provides significant performance

### AT A GLANCE

- Mixed-signal design engineers face increasing difficulties in design and verification of complex mixed-signal SOCs.

- ☑ Real-number modeling defines blocks in terms of input/output transfer characteristics, with no strong direct feedback present among the blocks.

- The digital world has many tools at its disposal—such as verification planning, coverage, and assertions—that can apply to analog verification given the right language extensions.

gains while retaining the right level of accuracy. The advantage of Verilog-A is the ability to use models in pure-analog simulations as well as in the mixed-signal environment. The models are too low-level, however, to enable efficient SOC-level verification of mixed-signal designs.

The RNM technique models electrical signals by representing them as real values. Provided that the modules are at a sufficiently high level of abstraction, the interfaces can be described by passing real numbers between blocks to represent the voltage, or current, signal being transferred. This is a powerful way to simulate complex systems rapidly. Traditionally, iterating to a solution involving feedback would require

an analog solver (see **sidebar**, "Analog versus digital solvers").

RNM is available in the Verilog-AMS, SystemVerilog, and VHDL-AMS languages. A commonly used RNM approach is the wreal data type in Verilog-AMS. RNM uses a discrete event solver—without an analog solver-and can be used to simulate mixedsignal systems at incredible speeds. It is primarily limited to modeling at a high enough level of abstraction that bidirectional analog interactions between blocks are not significant. In other words, typical RNM defines blocks in terms of input/output transfer characteristics, with no strong direct feedback present among the blocks. Logic can be modeled naturally in these languages, so RNM is also a good choice for systems with only a small amount of analog content.

### **TOP-DOWN OR BOTTOM-UP**

Designers use two principal methodologies based on the creation of behavioral models for mixed-signal design. In a top-down methodology, models are developed before the circuits are designed. The behavioral models can be simpler ones that are sufficient for functional verification at the system level. In a bottom-up methodology, the models are written to match an already implemented block for performance verification and usually result in a more accurate but slower-running model.

Figure 1 Results of a 2011 mixed-signal survey show that verification-related issues figure highly among customer challenges.

The creation of analog behavioral models can be challenging. Analog designers are in the best position to create such models because they are familiar with their own circuits. Many analog designers lack the programming skills and knowledge required to construct behavioral models, however, and few are familiar with Verilog or VHDL. Digital designers, conversely, have expertise with behavioral models but know less about analog circuits.

That dichotomy creates an opportunity for tool vendors to offer an automated or semi-automated solution for generating analog behavioral models. For example, automated, netlistdriven model-generation technologies can create a fairly accurate parametric behavioral model that considers PVT (process, voltage, and temperature) and loading variations for functional verification. Such an approach has shown some limited success on a subset of analog-circuit architectures under specific contexts, but there is still much work to be done to develop a general model-generation methodology with high accuracy that can be applied to any analog or mixed-signal design.

Creating behavioral models is only one part of the process of using those models in a mixed-signal verification flow. If the model and implementation do not match, the effort is worthless; worse, it can damage the entire design process. As a result, there is a need for a methodology to validate the accuracy of a behavioral model automatically against the corresponding design. The model also must be updated to keep it in sync with any changes made in the implementation.

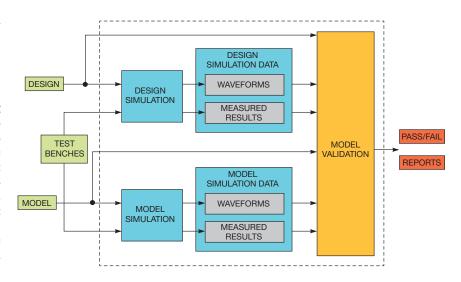

The model-validation flow shown in Figure 2 simulates the implementation and behavioral models using the same test bench, with the relevant tools and flows creating the required measuredresults behavior and waveform for each model. The designer can use the flow to validate that:

- The implementation- and behavioral-model measured results are within user-provided tolerances;

- The implementation- and behavioral-model waveforms are within userprovided tolerances; and

## **JOIN THE** CONVERSATION

To comment on this article, go to www.edn.com/4392246.

• Selected elements of the interfaces and pins of the behavioral and implementation models match.

This approach provides a selfcontained, automated analog-behavioral-model verification and debugging environment. The method lets users provide verification requirements through interactive configuration, and it uses the existing mixed-signal simulation setup to validate both the waveform signals and the measured results. Interactive verification-failure debug lets designers quickly identify problems in a model and rerun validation after fixing them.

That is just the beginning of the advantages that can be brought into the analog-verification world. The digital domain has many other tools at its disposal—such as verification planning, coverage, and assertions—that

## High Speed / Low Cost Development, Test & Burn-In Sockets

## Compression, SMT, &Thru-Hole PCB Mounting

Lead pitches as low as 0.4mm, up to 125,000 insertions.

Quick

Easy Screw - Lid removed to show detail.

## **Multi-Cavity Sockets**

Significantly reduce your socket & labor costs with these multiple IC test and burn-in solutions.

Easy Knob configuration

## **Custom Test Fixtures**

Fully automated or manually operated solutions to test any lead pitch & IC package

TECHNOLOGY, INC

1-800-232-7837 www.emulation.com

[www.edn.com] AUGUST 2012 | EDN 35 can apply to analog verification given the right language extensions.

#### **ASSERTIONS' ROLE**